AMDの次世代Ryzen 9050シリーズ「Strix Halo」APUの仕様については、しばらくの間噂が広まっていましたが、私たちを興奮させるいくつかの新しい詳細が明らかになりました。

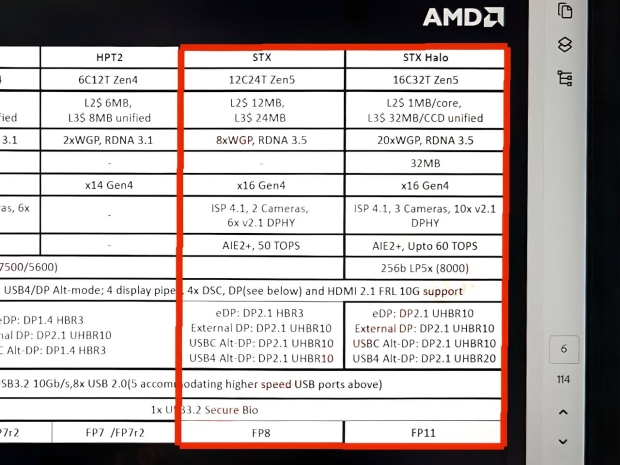

AMD の次世代 Strix Point および Strix Halo APU の仕様 (出典: HKEPC)

Advertisement

ギャラリーを見る – 2 枚の画像

新しい Strix Halo APU は、16 コアと 32 スレッドの次世代 Zen 5 処理能力を備え、コアあたり 1MB の L2 キャッシュと、CCD あたり 32MB の統合 L3 キャッシュ (MALL キャッシュ) を備えた非常に強力な APU になります。 Strix Halo APU には 1 つではなく 2 つの CCD が搭載されており、CCD あたり 8MB の L2 キャッシュが表示されます (CCD あたり 8 コア、2 つの CCD = 16 コア = 合計 16MB の L2 キャッシュ)。

AMD の次世代 Strix Halo APU は、AI ワークロード用にアップグレードされた XDNA2 ベースの NPU を搭載し、60 TOPS というはるかに高い AI ワークロード パフォーマンスを提供します。 覚えておいてください: これは NPU のみの 60 TOPS であり、Strix Halo の CPU と GPU からの機能は考慮されていません。 GPU について言えば、AMD には 20 個のワーク グループ プロセッサ (WGP) を備えた RDNA 3.5 ベースの GPU が含まれます。

Strix Halo にはハイエンド DisplayPort 2.1 UHBR10 および UHBR20 も搭載されており、次世代 APU を搭載したスーパーハイエンド ディスプレイの世界に対応します。 Strix Halo では 256 ビット LPDDR5X-8000 メモリをサポートしており、デフォルトでは TDP が 70 W ですが、トップエンドでは電力が 130 W までスケールアップされます。

Advertisement

一方、Strix Point はコア数を Zen 5 の処理能力の 12C/24T に、GPU を 8 WGP に減らしますが、それでもアップグレードされた RDNA 3.5 GPU アーキテクチャに基づいています。 Strix Point は見た目からすると LPDDR5X-7500 をサポートしますが、これはリリースが近づくと変更される可能性があります。

AMDは、6月5日に開幕するComputex 2024で、次世代のZen 5アーキテクチャと新しいRyzen 9000シリーズCPUを公開するはずだ。