Le président de TSMC, Mark Liu, et le scientifique en chef de TSMC, Philip Wong, ont co-écrit un nouvel article sur la route vers un GPU à 1 000 milliards de transistors.

VOIR LA GALERIE – 4 IMAGES

Advertisement

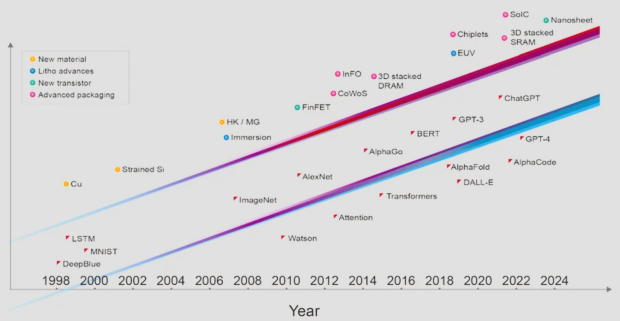

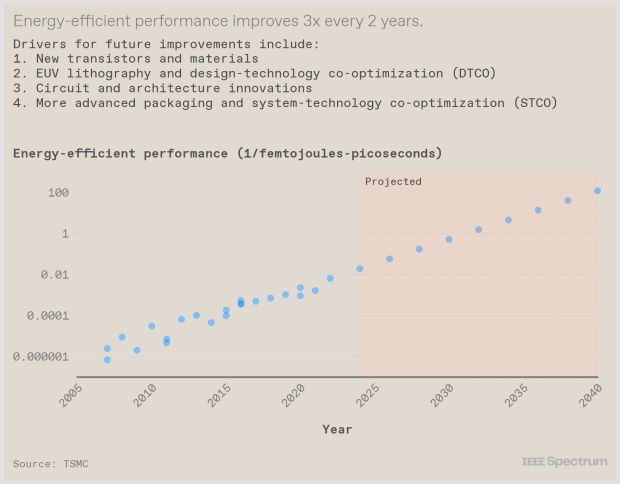

Les deux dirigeants de Taiwan Semiconductor Manufacturing Company (TSMC) ont souligné l'importance du conditionnement avancé des semi-conducteurs (CoWoS, SoIC, etc.) et le rôle vital que la photonique sur silicium jouera dans l'augmentation des vitesses de transfert de données entre les puces. Les deux dirigeants de TSMC ont écrit que si la révolution de l'IA doit se poursuivre au rythme actuel, « il faudra encore plus de la part de l'industrie des semi-conducteurs« .

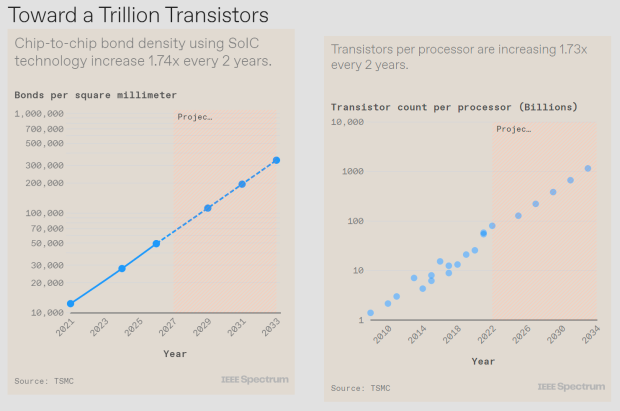

D’ici 10 ans, les dirigeants de TSMC ont déclaré que nous aurons besoin d’un GPU doté de 1 000 milliards de transistors, soit un GPU avec 10 fois plus de transistors qu’aujourd’hui. Le nouveau GPU Blackwell B200 AI de NVIDIA possède 208 milliards de transistors avec une conception en chipset et deux GPU distincts avec 104 milliards de transistors par puce. Il sera incroyable de voir 1 000 milliards de transistors se déployer sous nos yeux au cours des 5 à 6 prochaines années.

Depuis l’invention du circuit intégré, la technologie des semi-conducteurs s’est concentrée sur la réduction de la taille des fonctionnalités afin que les entreprises puissent intégrer autant de transistors que possible dans une puce de la taille d’une miniature. Aujourd'hui, l'intégration ne s'est pas arrêtée et des entreprises comme TSMC sont passées de la mise à l'échelle 2D à l'intégration de systèmes 3D : en plaçant autant de puces dans un système étroitement intégré et massivement interconnecté.

TSMC dispose de sa technologie d'emballage avancée Chip-on-Wafer-on-Substrate (CoWoS), capable d'adapter 6 champs de réticule de puces de calcul, ainsi que 12 puces mémoire HBM. L'une des limites des outils de fabrication de puces lithographiques est qu'ils ont été conçus pour fabriquer des circuits intégrés (circuits intégrés) dont la taille ne dépasse pas environ 800 millimètres carrés, ce que l'on appelle la « limite du réticule ».

Advertisement

Les dirigeants de TSMC expliquent qu'ils peuvent désormais étendre la taille du système intégré « au-delà de la limite du réticule de la lithographie » en attaquant plusieurs puces plus grandes sur un interposeur plus grand, qui est un morceau de silicium dans lequel les interconnexions sont intégrées, permettant ainsi à TSMC et à d'autres sociétés d'emballage avancées intégrer un système contenant un nombre de périphériques beaucoup plus important que ce qui est possible avec une seule puce.

Le nouveau GPU Blackwell B200 AI de NVIDIA en est le meilleur exemple, avec 208 milliards de transistors au total – fabriqués chez TSMC sur son nouveau nœud de processus N4P – avec une conception à double chiplet qui comprend deux puces GPU de la taille d'un réticule. NVIDIA est passé d'un GPU monolithique à une conception basée sur des chipsets, avec un énorme 208 milliards de transistors pour le B200, soit 104 milliards de transistors.

Ce ne sont pas seulement les GPU qui sont importants pour l’avenir – en particulier celui de l’IA – de l’industrie des semi-conducteurs, comme HBM. La mémoire HBM comporte une pile de puces DRAM interconnectées verticalement au-dessus d'un circuit intégré logique de contrôle. Il utilise des interconnexions verticales appelées through-silicon-via (TSV) pour faire passer les signaux à travers chaque puce et des bosses de soudure pour former les connexions entre les puces mémoire. Les meilleurs GPU IA hautes performances au monde utilisent tous exclusivement HBM, avec la mémoire HBM3 et maintenant HBM3E.

Advertisement

TSMC explique que la technologie 3D SoIC offrira une « alternative sans problème » à la technologie HBM conventionnelle d'aujourd'hui, où elle offrira « une interconnexion verticale beaucoup plus dense entre les puces empilées ». Nous avons récemment vu une présentation de la mémoire HBM3E à 12 couches, dont les structures de test HBM avec 12 couches de puces empilées utilisent une liaison hybride, une connexion cuivre à cuivre avec une densité supérieure à celle dont sont capables les bosses de soudure. Lié à basse température sur une puce logique de base plus grande, ce système de mémoire a une épaisseur totale de seulement 600 µm.

Les dirigeants de TSMC ont expliqué comment arriver à 1 000 milliards de GPU à transistors : « Comme nous l'avons déjà indiqué, les puces GPU typiques utilisées pour la formation de l'IA ont déjà atteint la limite du champ de réticule. Et leur nombre de transistors est d'environ 100 milliards d'appareils. La tendance à l'augmentation du nombre de transistors se poursuit. Le nombre de transistors nécessitera plusieurs puces, interconnectées avec une intégration 2,5D ou 3D, pour effectuer le calcul. L'intégration de plusieurs puces, soit par CoWoS, soit par SoIC et les technologies de conditionnement avancées associées, permet un nombre total de transistors par système beaucoup plus important que celui qui peut être compressé. en une seule puce. Nous prévoyons que d'ici une décennie, un GPU multichiplet comportera plus de 1 000 milliards de transistors ».

« Nous devrons relier tous ces chipsets ensemble dans une pile 3D, mais heureusement, l'industrie a pu rapidement réduire le nombre d'interconnexions verticales, augmentant ainsi la densité des connexions. Et il reste encore beaucoup de place pour plus. Nous voyons Il n'y a aucune raison pour que la densité des interconnexions ne puisse pas croître d'un ordre de grandeur, et même au-delà ».

Advertisement