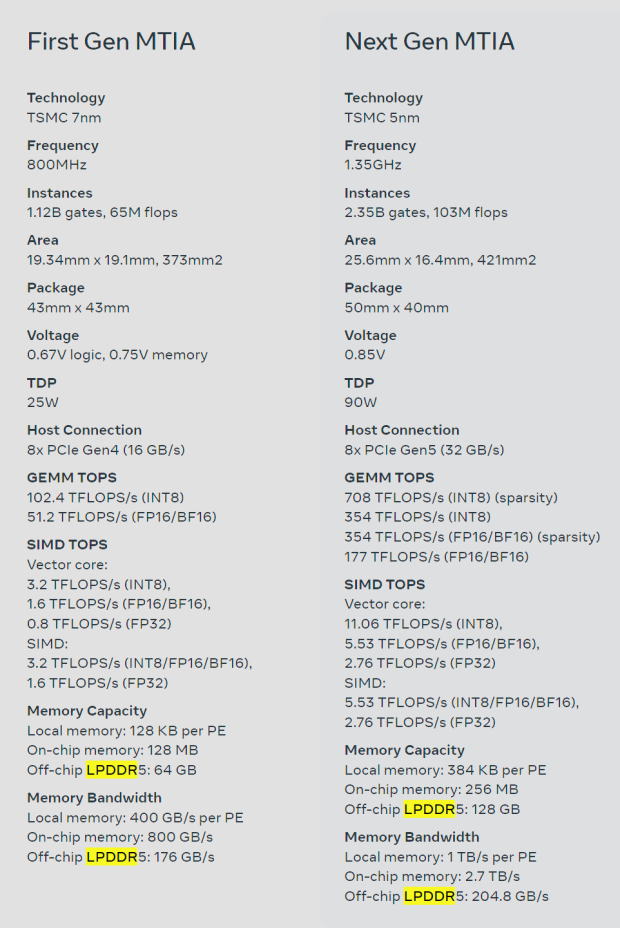

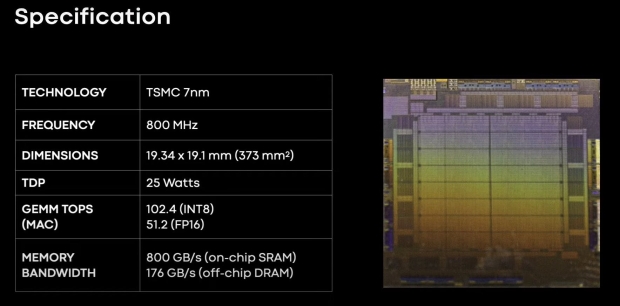

Meta は、現在の MTIA v1 チップをアップグレードした次世代 AI チップである MTIA を公開しました。 新しいMTIAチップはTSMCの新しい5nmプロセスノードで作られており、オリジナルのMTIAチップは7nmで作られています。

ギャラリーを見る – 3 枚の画像

Advertisement

新しい Meta Training and Inference Accelerator (MTIA) チップは、Meta の固有の要件に使用される「コンピューティング、メモリ帯域幅、メモリ容量の適切なバランスを提供することに基本的に重点を置いています」。 NVIDIA の Hopper H100 および AMD Instinct MI300 シリーズ AI チップで使用されている HBM3 と、サーバー DRAM または LPDDR5 メモリの代わりに低電力 DRAM メモリ (LPDDR5) を使用する Meta を備えた、HBM メモリを使用する地球上で最高の AI GPU を見てきました。 。

ソーシャル ネットワーキングの巨人である同社が開発した MTIA チップは、同社の第 1 世代 AI 推論アクセラレータであり、Meta の AI ワークロードを念頭に置いて社内で設計されました。 同社は、深層学習レコメンデーションモデルにより「当社製品全体のさまざまなエクスペリエンスが向上している」と述べている。

Meta の長期的な目標と AI 推論プロセッサの取り組みは、Meta の独自のワークロードに最も効率的なアーキテクチャを提供することです。 Meta の製品とサービスにとって AI ワークロードの重要性が高まるにつれ、MTIA チップの効率が向上し、世界中のユーザーに最高のエクスペリエンスを提供する能力が向上すると同社は付け加えています。

Meta は MTIA の Web サイトで次のように説明しています。「このチップのアーキテクチャは基本的に、ランキングおよび推奨モデルを提供するために、コンピューティング、メモリ帯域幅、およびメモリ容量の適切なバランスを提供することに重点を置いています。推論では、比較的高い使用率を提供できる必要があります。 「バッチ サイズが比較的小さい場合。一般的な GPU と比べて特大の SRAM 容量を提供することに重点を置くことで、バッチ サイズが制限されている場合でも高い使用率を提供し、潜在的な同時作業量が増加した場合でも十分なコンピューティングを提供できます。」

Advertisement

「このアクセラレータは、8×8 グリッドのプロセッシング エレメント (PE) で構成されています。これらの PE は、高密度コンピューティング パフォーマンス (MTIA v1 の 3.5 倍) とスパース コンピューティング パフォーマンス (7 倍の向上) を大幅に向上させます。これは、部分的には、パイプライン化に関連するアーキテクチャの改善によるものです。」これは、PE グリッドへの供給方法からも来ています。ローカル PE ストレージのサイズを 3 倍にし、オンチップ SRAM を 2 倍にし、帯域幅を 3.5 倍に増加させ、LPDDR5 の容量を 2 倍にしました。