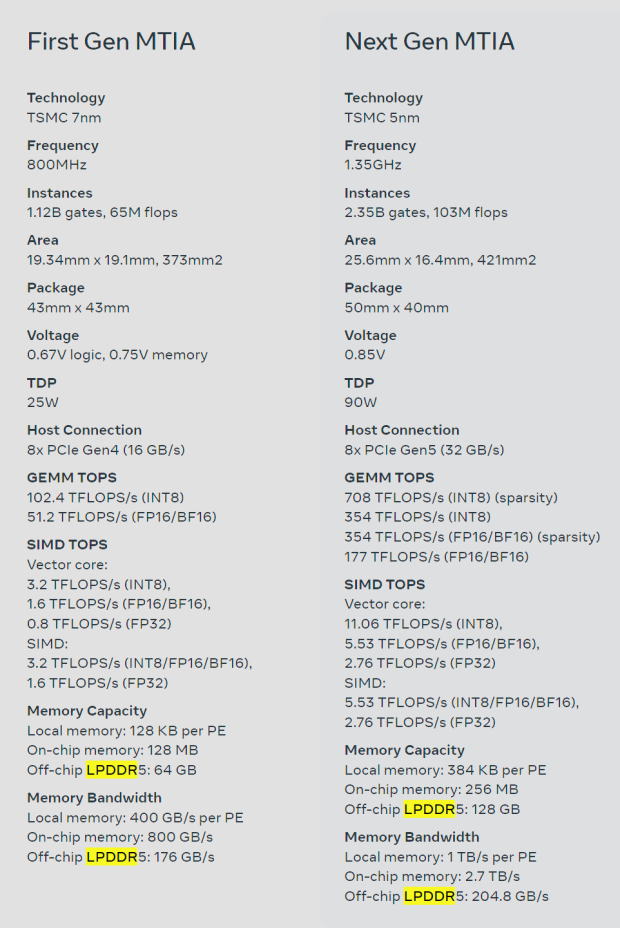

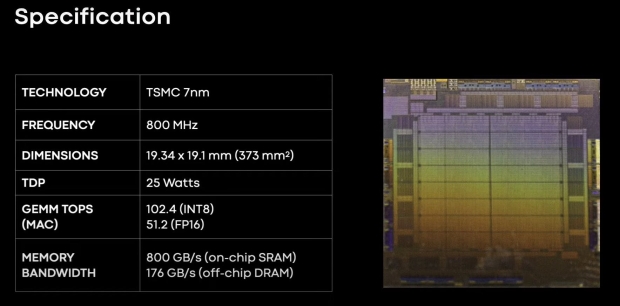

Meta ha appena presentato in anteprima il suo chip AI di prossima generazione, MTIA, che rappresenta un aggiornamento rispetto all'attuale chip MTIA v1. Il nuovo chip MTIA è realizzato sul nuovo nodo di processo a 5 nm di TSMC, con il chip MTIA originale realizzato su 7 nm.

VISUALIZZA GALLERIA – 3 IMMAGINI

Il nuovo chip Meta Training and Inference Accelerator (MTIA) è “fondamentalmente focalizzato nel fornire il giusto equilibrio tra elaborazione, larghezza di banda della memoria e capacità di memoria” che verrà utilizzato per i requisiti unici di Meta. Abbiamo visto le migliori GPU AI del pianeta utilizzare la memoria HBM – con HBM3 utilizzato sui chip AI della serie Hopper H100 e AMD Instinct MI300 di NVIDIA – con Meta che utilizza memoria DRAM a basso consumo (LPDDR5) invece della DRAM del server o della memoria LPDDR5 .

Il gigante dei social network ha creato il suo chip MTIA, l'acceleratore di inferenza AI di prima generazione dell'azienda che l'azienda ha progettato internamente pensando al carico di lavoro AI di Meta. L'azienda afferma che i suoi modelli di raccomandazione sul deep learning stanno “migliorando una varietà di esperienze attraverso i nostri prodotti”.

Advertisement

L'obiettivo a lungo termine di Meta e il percorso intrapreso dal processore di inferenza AI sono fornire l'architettura più efficiente per i carichi di lavoro unici di Meta. L'azienda aggiunge che poiché i carichi di lavoro dell'intelligenza artificiale diventano sempre più importanti per i prodotti e i servizi di Meta, l'efficienza dei suoi chip MTIA migliorerà la sua capacità di fornire le migliori esperienze ai suoi utenti in tutto il pianeta.

Meta spiega sul suo sito web per MTIA: “L'architettura di questo chip è fondamentalmente focalizzata nel fornire il giusto equilibrio tra elaborazione, larghezza di banda della memoria e capacità di memoria per servire modelli di classificazione e raccomandazione. In deduzione dobbiamo essere in grado di fornire un utilizzo relativamente elevato, anche quando le dimensioni dei nostri batch sono relativamente basse. Concentrandoci sulla fornitura di capacità SRAM fuori misura, rispetto alle GPU tipiche, possiamo fornire un utilizzo elevato nei casi in cui le dimensioni dei batch sono limitate e fornire elaborazione sufficiente quando si verificano quantità maggiori di potenziale lavoro simultaneo”.

Advertisement

“Questo acceleratore è costituito da una griglia 8×8 di elementi di elaborazione (PE). Questi PE forniscono prestazioni di calcolo denso significativamente aumentate (3,5 volte rispetto a MTIA v1) e prestazioni di calcolo sparse (miglioramento 7 volte). Ciò deriva in parte da miglioramenti nell'architettura associata al pipeline Il problema deriva anche dal modo in cui alimentiamo la rete PE: abbiamo triplicato le dimensioni dello storage PE locale, raddoppiato la SRAM su chip e aumentato la sua larghezza di banda di 3,5 volte e raddoppiato la capacità di LPDDR5”.